## **ECE 3040 Microelectronic Circuits**

Exam 3

April 21, 2017

Dr. W. Alan Doolittle

Print your name clearly and largely:

Solutions

Instructions:

**DO NOT TAKE APART ANY PAGES OF THIS EXAM AND SHOW ALL WORK ON** <u>**THE PROVIDED PAGES.</u>** Read all the problems carefully and thoroughly before you begin working. You are allowed to use 1 new sheet of notes (1 page front and back), your two note sheets from the previous exams as well as a calculator. There are 100 total points in this exam. Observe the point value of each problem and allocate your time accordingly. SHOW ALL WORK AND CIRCLE YOUR FINAL ANSWER WITH THE PROPER UNITS INDICATED. Write legibly. If 1 cannot read it, it will be considered a wrong answer. Do all work on the paper provided. Turn in all scratch paper, even if it did not lead to an answer. Report any and all ethics violations to the instructor. Good luck!</u>

Sign your name on **ONE** of the two following cases:

I DID NOT observe any ethical violations during this exam:

I observed an ethical violation during this exam:

## First 24% Multiple Choice and True/False (Select the most correct answer)

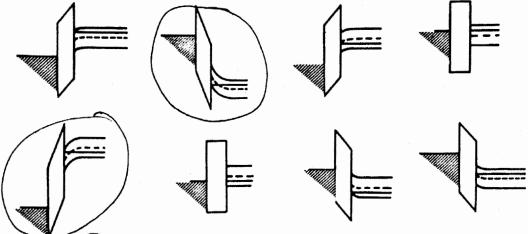

1.) (6-points total) For the MOS Capacitors shown below, Circle the correct capacitor bias mode that corresponds to a MOSFET Bias mode of Saturation

- 2.) (3-points) True) False: Feedback can increase the closed loop bandwidth of an opamp.

- 3.) (3-points) True) False: When a MOSFET channel is "pinched-off", regardless of the length of the drain voltage V<sub>DS</sub>, the end of the channel is at V<sub>DSAT</sub>.

- 4.) (3-points) True / False: A PMOS transistor has a p-type drain.

- 5.) (3-points) True / False: A well designed current amplifier should have a very high input resistance.

- 6.) (3-points) True/False: A Common Drain amplifier has a negative gain whose magnitude can be greater than 1.

- 7.) (3-points) True/False: Minority carriers dominate MOSFET current flow in saturation.

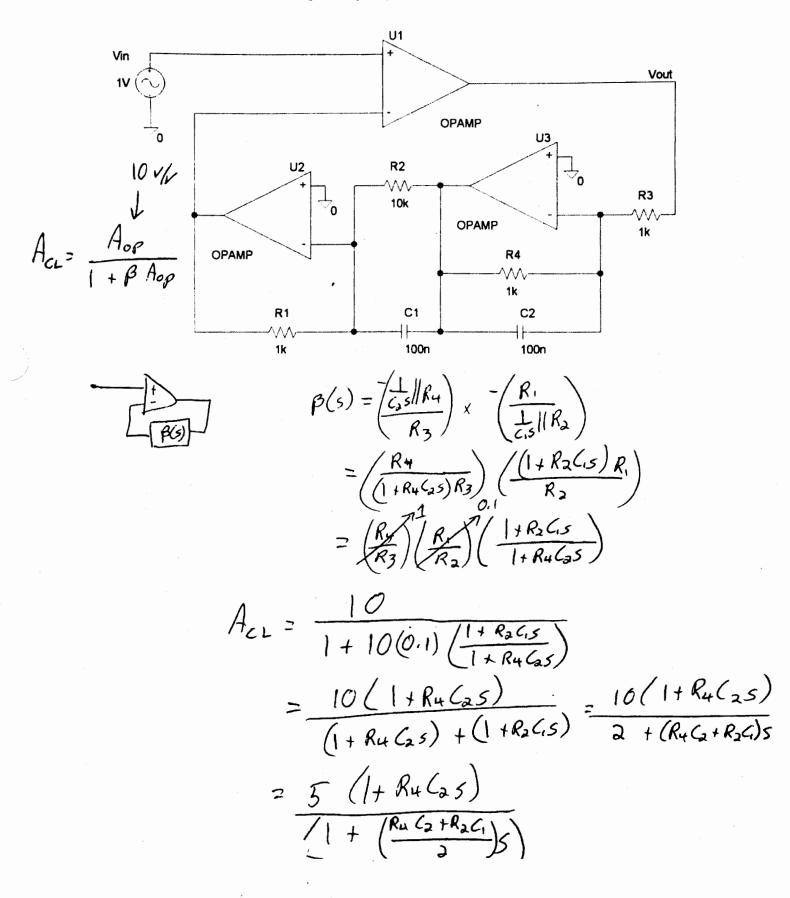

8.) (26-points) The opamps used in the circuit below can be considered ideal except U1 (and only U1) has an open loop gain of only 10 volts/volt. Determine the closed loop gain and sketch and label the Bode plot showing the voltage gain in all flat regions and the break frequencies (gain in dB vs Log of Frequency).

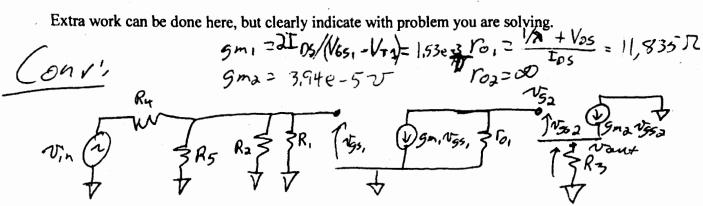

Extra work can be done here, but clearly indicate with problem you are solving.

Pulling all the concepts together for a useful purpose:

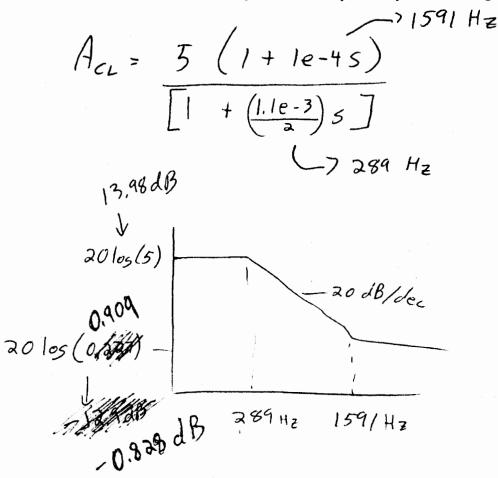

<u>10) (50-points)</u> Given the following amplifier circuit, (a) Identify the configuration of the stage (common \_\_\_\_). (b) What is the AC voltage gain,  $v_{out}/v_{in}$ ? You may assume all capacitors have infinite capacitance and all inductors have infinite inductance. Additionally consider the circuit to be operated at low frequencies where you can neglect all small signal capacitances.

Grading will be based as such: part a=5 points, part b=18 points for DC solution (gate, source and drain voltages along with drain currents), 12 points for the conversion to the small signal model and 15 points for small signal analysis. <u>SHOW ALL WORK TO</u> <u>GET CREDIT!!!!! Do not just quote a result!!!!!</u>

Use the following parameters (note that K,  $V_T$  and  $\lambda$  vary with transistor type):

| M2'.   | For NMOS Dep $\zeta_n$ '=15 uA/V <sup>2</sup> | letion Transisto<br>V <sub>T</sub> = -4.0V | ors:<br>λ=0.0 V <sup>-1</sup>     | Length (L)=10 um | Width (W)=10 um |

|--------|-----------------------------------------------|--------------------------------------------|-----------------------------------|------------------|-----------------|

| M1;    | For NMOS Enh<br>Kn'=250 uA/V <sup>2</sup>     | ancement Trans<br>V <sub>T</sub> = +1.0V   | sistors:<br>λ=0.1 V <sup>-1</sup> | Length (L)=10 um | Width (W)=10 um |

| F<br>K | for PMOS Depl<br>(p'=40 uA/V <sup>2</sup>     | etion Transistor<br>V <sub>T</sub> = +3.0V | rs:<br>λ=0.0 V <sup>-1</sup>      | Length (L)=10 um | Width (W)=10 um |

|        |                                               | incement Transition $V_T = -1.75V$         |                                   | Length (L)=10 um | Width (W)=10 um |

Extra work can be done here, but clearly indicate with problem you are solving.

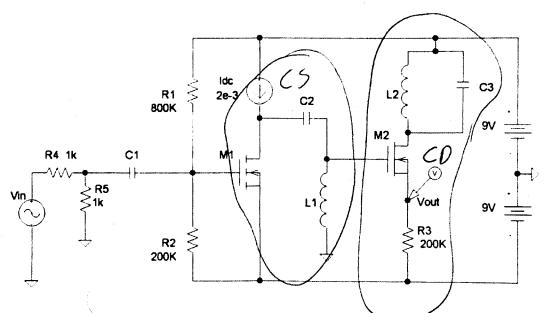

DC Solution Voes not matter MI:  $\begin{array}{cccc}

T & T & V_{65} \\

(w/L) & t_n' & V_{65}

\end{array}$  $V_{0s} = 13,668V \longrightarrow V_0 = V_{0s} + q_V = 4,668V$   $Gaturation V_{0s} = V_{6s} - V_T$ 13,67> 3,6-1 Vo=0 Vs=-9+IosR3 Ma: 16=0  $I_{05} = \binom{10}{10} \binom{15e-6}{2} \binom{165-14}{10} \binom{1}{10} \binom$ V65= V6-V5 -9-JosR3 (w/L) K  $or I_{OS} = \left( \frac{7 - V_{GS}}{\rho_{T}} \right)$  $\left(\frac{9-V_{65}}{P_{7}}\right) = (7.5e-6)\left(V_{65}^2 - 2V_{65}V_{7} + V_{7}^2\right)$  $O = 7.5e - 6V_{6s}^{2} + (8(7.5e - 6) + \frac{1}{200}\pi)V_{6s} + [16(7.5e - 6) - 9]$ V65= - 1.37V or - 7.30K = I05 = 51.85 m A L> Cutoff  $V_{5} = 1.37V$  -1.37 - (-4) = 2.631  $V_{05} = 9 - 1.37V = 7.63V > V_{65} - VT$ Sat umto

1)  $\frac{N_{550}}{V_{10}} = \left(\frac{R_5 ||R_2||R_1}{R_1 + R_5 ||R_2||R_1}\right) = 0.5$

2)  $\frac{V_{go2}}{V_{es1}} = -(g_m, f_m, r_0) = -18.1$ 3)  $V_{52} = V_{552} + R_3 g_{n2} V_{552} = V_{552} (1 + g_{m_2} R_3)$ 7.88 4)  $V_{0ut} = g_{m_2} R_3 v_{952}$ 8.88

$= (0.5)(-16.1)(\frac{3}{9.88})(\frac{4}{7.88})$  [Av = -8.03 v/v]