#### Lecture 25

**MOSFET Basics (Understanding with Math)**

Reading: Pierret 17.1-17.2 and Jaeger 4.1-4.10 and Notes

Georgia Tech ECE 3040 - Dr. Alan Doolittle

With our expression relating the Gate voltage to the surface potential and the fact that  $\phi_S = 2\phi_F$  we can determine the value of the threshold voltage

$$V_{T} = 2\phi_{F} + \frac{\varepsilon_{S}}{C_{ox}} \sqrt{\frac{2qN_{A}}{\varepsilon_{S}}} (2\phi_{F}) \quad \text{(for n - channel devices)}$$

$$V_{T} = 2\phi_{F} - \frac{\varepsilon_{S}}{C_{ox}} \sqrt{\frac{2qN_{D}}{\varepsilon_{S}}} (-2\phi_{F}) \quad \text{(for p - channel devices)}$$

$$V_T = 2\phi_F - \frac{\varepsilon_S}{C_{ox}} \sqrt{\frac{2qN_D}{\varepsilon_S} (-2\phi_F)}$$

(for p - channel devices)

where,

$$C_{ox} = \frac{\mathcal{E}_{ox}}{x_{ox}}$$

is the oxide capacitance per unit area

Where we have made use of the use of the expression,

$$\varepsilon_{S} = K_{S} \varepsilon_{o}$$

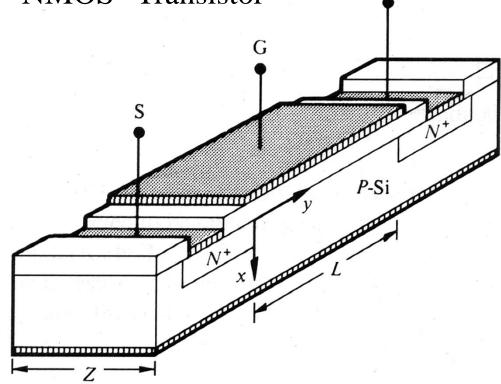

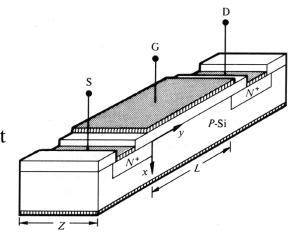

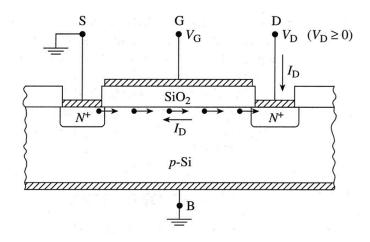

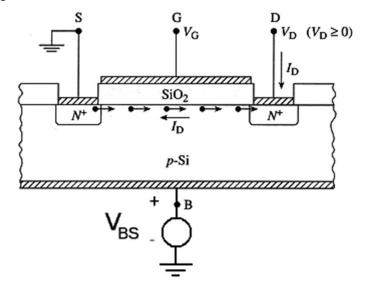

Coordinate Definitions for our "NMOS" Transistor

x=depth into the semiconductor from the oxide interface.

y=length along the channel from the source contact

z=width of the channel

$x_c(y)$  = channel depth (varies along the length of the channel).

n(x,y)= electron concentration at point (x,y)

$\mu_n(x,y)$ =the mobility of the carriers at point (x,y)

Device width is Z

Channel Length is L

Assume a "Long Channel" device (for now do not worry about the channel length modulation effect) ECE 3040 - Dr. Alan Doolittle

## Concept of Effective mobility

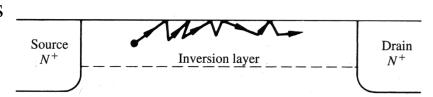

The mobility of carriers near the interface is significantly lower than carriers in the semiconductor bulk due to interface scattering.

Since the electron concentration also varies with position, the average mobility of electrons in the channel, known as the effective mobility, can be calculated by a weighted average,

$$\overline{\mu_n} = \frac{\int_{x=0}^{x=x_c(y)} \mu_n(x, y) n(x, y) dx}{\int_{x=0}^{x=x_c(y)} n(x, y) dx}$$

or defining,

$Q_N(y) = -q \int_{x=0}^{x=x_c(y)} n(x, y) dx \quad \left[ ch \arg e / cm^2 \right]$

$$\overline{\mu_n} = \frac{-q}{Q_N(y)} \int_{x=0}^{x=x_c(y)} \mu_n(x, y) n(x, y) dx$$

Georgia Tech

**Empirically**

$$\frac{\overline{\mu_n}}{\overline{\mu_n}} = \frac{\mu_o}{1 + \theta \left( V_{GS} - V_T \right)}$$

where,  $\mu_o$  and  $\theta$  are constants

## Drain Current-Voltage Relationship

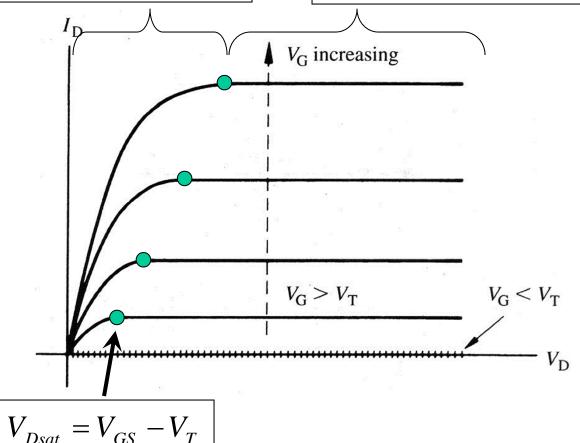

In the Linear Region,  $V_{GS} > V_{T}$  and  $0 < V_{DS} < V_{dsat}$

$$J_N = q\mu_n nE + qD_N \nabla n$$

Neglecting the diffusion current, and recognizing the current is only in the y-direction,

$$J_N \cong J_{Ny} \cong q\mu_n nE_y \cong -q\mu_n n\frac{d\phi}{dy}$$

Drain Current-Voltage Relationship

In the Linear Region,  $V_{GS} > V_T$  and  $0 < V_{DS} < V_{dsat}$

$$I_D = -\int \int J_{Ny} dx dz = Z \int_{x=0}^{x=x_c(y)} J_{Ny} dx$$

$$= \left(-Z\frac{d\phi}{dy}\right)\left(-q\int_{x=0}^{x=x_c(y)}\mu_n(x,y)n(x,y)dx\right)$$

$$= -Z\overline{\mu_n}Q_N \frac{d\phi}{dy}$$

$$\int_{y=0}^{y=L} I_D dy = -Z \overline{\mu_n} \int_{\phi=0}^{\phi=V_{DS}} Q_N d\phi$$

$$I_D L = -Z \overline{\mu_n} \int_{\phi=0}^{\phi=V_{DS}} Q_N d\phi$$

$$I_{D} = \frac{-Z\overline{\mu_{n}}}{L} \int_{\phi=0}^{\phi=V_{DS}} Q_{N} d\phi$$

To find  $I_D$ , we need an expression relating the electrostatic potential,  $\phi$ , and  $Q_N$

Georgia Tech

ECE 3040 - Dr. Alan Doolittle

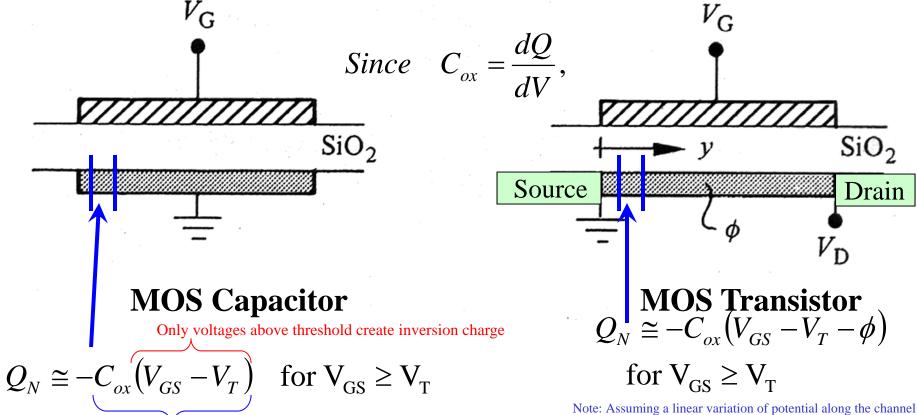

# "Capacitor-Like" Model for Q<sub>N</sub>

## Assumptions:

- •Neglect all but the mobile inversion charge (valid for deep inversion)

- •For the MOSFET, the charge in the semiconductor is a linear function of position along the semiconductor side of the plate. Thus,  $\phi$  varies from 0 to  $V_{DS}$

Neglect the depletion region charge Georgia Tech

Note: Assuming a linear variation of potential along the channel leads to an underestimation of current but is a good estimate for hand calculations.

ECE 3040 - Dr. Alan Doolittle

Using "Capacitor-Like" Model for  $Q_N$  we can estimate  $I_D$  as:

$$I_{D} = \frac{-Z\overline{\mu_{n}}}{L} \int_{\phi=0}^{\phi=V_{DS}} Q_{N} d\phi$$

$$I_{D} = \frac{-Z\overline{\mu_{n}}}{L} \int_{\phi=0}^{\phi=V_{DS}} -C_{ox} (V_{G} - V_{T} - \phi) d\phi$$

$$I_{D} = \frac{Z\overline{\mu_{n}}C_{ox}}{L} \left[ \left( V_{GS} - V_{T} \right) V_{DS} - \frac{V_{DS}^{2}}{2} \right] \qquad 0 \le V_{DS} \le V_{Dsat} \quad and \quad V_{GS} \ge V_{T}$$

This is known as the "square law" describing the Current-Voltage characteristics in the "Linear" or "Triode" region.

Note the linear behavior for small  $V_{DS}$  (can neglect  $V_{DS}^2$  term). Note the negative parabolic dependence for larger  $V_{DS}$  but still  $V_{DS} < V_{Dsat}$  (can NOT neglect  $V_{DS}^2$  term).

## "Capacitor-Like" Model for Q<sub>N</sub>

But what about the saturation region?

For  $V_{DS} > V_{dsat}$  the voltage drop across our channel is  $V_{Dsat}$  with the remaining voltage  $(V_{DS} - V_{Dsat})$  dropped across the pinch-off region

$$I_{D} = I_{Dsat} = \frac{Z\overline{\mu_{n}}C_{ox}}{L} \left[ (V_{GS} - V_{T})V_{Dsat} - \frac{V_{Dsat}^{2}}{2} \right] \qquad V_{Dsat} \leq V_{DS}$$

But the charge at the end of the channel is zero due to the pinched off channel,

$$Q_{N}(y = L) \cong -C_{ox}(V_{GS} - V_{T} - V_{Dsat}) = 0$$

$$Or$$

$$V_{GS} - V_{T} = V_{Dsat}$$

Thus,

$$I_D = I_{Dsat} = \frac{Z\overline{\mu_n}C_{ox}}{2L} \left[ (V_{GS} - V_T)^2 \right] \qquad V_{Dsat} \le V_{DS}$$

## MOS Transistor I-V Derivation Summary of MOSFET IV Relationship

$$I_{D} = \frac{Z\overline{\mu_{n}}C_{ox}}{L} \left[ (V_{GS} - V_{T})V_{DS} - \frac{V_{DS}^{2}}{2} \right]$$

$$0 \le V_{DS} \le V_{Dsat} \quad and \quad V_{GS} \ge V_{T}$$

$$I_D = I_{Dsat} = \frac{Z\overline{\mu_n}C_{ox}}{2L} \left[ (V_{GS} - V_T)^2 \right] \qquad V_{Dsat} \le V_{DS}$$

Georgia Tech

ECE 3040 - Dr. Alan Doolittle

## **MOS** Transistor Applications

## **Voltage variable Resistor**

An n-channel MOSFET has a gate width to length ratio of Z/L=100,  $u_n=200$  cm²/Vsec, Cox=0.166 uF/cm² and  $V_T=1V$ . We want to develop a resistor that has a resistance that is controlled by an external voltage. Such a device would be used in "variable gain amplifiers", "automatic gain control devices", "compressors" and many other electronic devices. Define what range of  $V_{DS}$  must be maintained to achieve proper "voltage variable resistance" operation. Find the "On-resistance"  $(V_{DS}/I_D)$  of the transistor from 1.5V< $V_{GS}$ <4Vfor small  $V_{DS}$ .

First, to achieve voltage variable resistance operation, we must operate in the linear region. Otherwise, the current is either a constant regardless of drain voltage (saturation region) or is approximately zero (cutoff due to the capacitor being in either accumulation and depletion).

Thus,  $V_{GS} - V_T > V_{DS}$ . Given the values above,  $0 < V_{DS} < 0.5V$

Continued...

ECE 3040 - Dr. Alan Doolittle

## **MOS** Transistor Applications

## **Voltage variable Resistor**

Using the linear region  $I_D$  equation:

$$I_{D} = \frac{Z\overline{\mu_{n}}C_{ox}}{L} \left[ (V_{GS} - V_{T})V_{DS} - \frac{V_{DS}^{2}}{2} \right] \approx \frac{Z\overline{\mu_{n}}C_{ox}}{L} \left[ (V_{GS} - V_{T})V_{DS} \right] \quad \text{for small } V_{DS}$$

$$R_{DS} = \frac{V_{DS}}{I_{D}} = \frac{V_{DS}}{\frac{Z\overline{\mu_{n}}C_{ox}}{L}[(V_{GS} - V_{T})V_{DS}]} = \frac{\frac{L}{Z}}{\overline{\mu_{n}}C_{ox}[(V_{GS} - V_{T})]}$$

$$R_{DS} = \frac{0.01}{200(0.166e - 6F / cm^2)[(V_{GS} - 1)]}$$

Thus,

$$100~\Omega \le R_{DS} \le 600~\Omega$$

## **MOS** Transistor Applications

#### **Current Source**

The same transistor is to be used for a "Current Source". Define the range of drain-source voltage that can be used to achieve a fixed current of 50 uA.

For a constant current regardless of Drain-Source voltage, we must use the saturation region:

$$I_{D} = I_{Dsat} = \frac{Z \mu_{n} C_{ox}}{2L} [(V_{GS} - V_{T})^{2}] \qquad V_{Dsat} \leq V_{DS}$$

$$50uA = \frac{100(200cm^{2} / VSec)0.166uF / cm^{2}}{2} (V_{GS} - 1)^{2}$$

$$V_{GS} = 1.173V$$

This source will operate over a  $V_{DS} > V_{GS} - V_T$  or  $V_{DS} > 0.173 \text{ V}$

Georgia Tech

ECE 3040 - Dr. Alan Doolittle

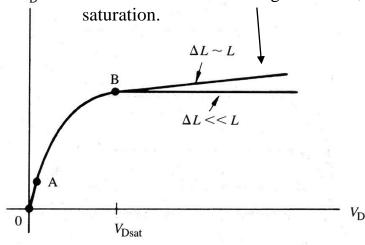

#### Channel Length Modulation Effect

Above "pinch-off" (when  $V_{DS}>V_{Dsat}=V_{GS}-V_{T}$ ) the channel length reduces by a value  $\Delta L$ .

Thus, the expression for drain current,

$$I_{D} = I_{Dsat} = \frac{Z\overline{\mu_{n}}C_{ox}}{2L} \left[ \left( V_{GS} - V_{T} \right)^{2} \right] \qquad V_{Dsat} \leq V_{DS}$$

Becomes,

$$I_{D} = I_{Dsat} = \frac{Z\mu_{n}C_{ox}}{2(L - \Delta L)} \left[ (V_{GS} - V_{T})^{2} \right] \qquad V_{Dsat} \leq V_{DS}$$

or since \*  $\Delta L \langle L, \frac{1}{L - \Delta L} \cong \frac{1}{L} \left( 1 + \frac{\Delta L}{L} \right)$

$$I_{D} = I_{Dsat} = \frac{Z\overline{\mu_{n}}C_{ox}}{2L} \left[ (V_{GS} - V_{T})^{2} \right] \left( 1 + \frac{\Delta L}{L} \right) \qquad V_{Dsat} \leq V_{DS}$$

<sup>\*</sup>In many modern devices, this assumption does not hold. Thus, the channel length modulation parameter we are deriving does not describe the IV expressions well.

#### Channel Length Modulation Effect

But the fraction of the channel that is pinched off depends linearly on  $V_{DS}$  because the voltage across the pinch-off region is  $(V_{DS}-V_{Dsat})$  so,

$$\frac{\Delta L}{L} = \lambda V_{DS}$$

where  $\lambda$  is known as the *Channel-Length Modulation parameter* and is typically:  $0.001 \text{ V}^{-1} < \lambda < 0.1 \text{ V}^{-1}$

Channel Length Modulation causes the dependence of drain current on the drain voltage in saturation.

$$I_{D} = I_{Dsat} = \frac{Z\overline{\mu_{n}}C_{ox}}{2L} [(V_{GS} - V_{T})^{2}] (1 + \lambda V_{DS})$$

$V_{Dsat} \leq V_{DS}$

Body Effect (Substrate Biasing)

Until now, we have only considered the case where the substrate (Body) has been grounded....

...but the substrate (Body) is often intentionally biased such that the Source-Body and Drain-Body junctions are reversed biased.

The body bias,  $V_{BS}$ , is known as the *backgate bias* and can be used to modify the threshold voltage.

Note that now our channel potential has an offset equal to  $V_{BS}$ , ....

#### Body Effect (Substrate Biasing)

Thus, our threshold potential with the body grounded,

$$V_T = 2\phi_F + \frac{\varepsilon_S}{C_{ox}} \sqrt{\frac{2qN_A}{\varepsilon_S} (2\phi_F)} \quad \text{(for n-channel devices)}$$

$$V_T = 2\phi_F - \frac{\varepsilon_S}{C_{ox}} \sqrt{\frac{2qN_D}{\varepsilon_S} \left(-2\phi_F\right)} \quad \text{(for p-channel devices)}$$

Surface Potential  $\phi_S$

The Gate-Body Threshold becomes,

$$V_{GB|_{Threshold}} = 2\phi_F - V_{BS} + \frac{\varepsilon_S}{C_{ox}} \sqrt{\frac{2qN_D}{\varepsilon_S} \left(2\phi_F - V_{BS}\right)} \quad \text{(for p-channel devices)} \quad \text{VBS} \quad \frac{1}{2} \sum_{k=0}^{\infty} \frac{1}{2} \left(2\phi_F - V_{BS}\right)$$

$$V_{GB|_{Threshold}} = 2\phi_F - V_{BS} - \frac{\varepsilon_S}{C_{ox}} \sqrt{\frac{2qN_A}{\varepsilon_S} \left(-2\phi_F + V_{BS}\right)} \quad \text{(for n - channel devices)}$$

But we would like to have this in terms of  $V_{GS}$  instead of  $V_{GB}$ .

Since,

$$V_{GS} = V_{GB} + V_{BS}$$

$$\mathbf{V}_{\mathbf{T}} = \begin{cases} V_{GS|_{Threshold}} = 2\phi_F + \frac{\varepsilon_S}{C_{ox}} \sqrt{\frac{2qN_A}{\varepsilon_S}} \left(2\phi_F - V_{BS}\right) & \text{(for n - channel devices)} \\ V_{GS|_{Threshold}} = 2\phi_F - \frac{\varepsilon_S}{C_{ox}} \sqrt{\frac{2qN_D}{\varepsilon_S}} \left(-2\phi_F + V_{BS}\right) & \text{(for p - channel devices)} \end{cases}$$

#### Body Effect (Substrate Biasing)

This can be rewritten in the following form (more convenient to reference the threshold voltage to the  $V_{BS}$ =0 case).

$$\begin{split} &V_{T}\big(Pierret\big) = V_{TN}\big(Jaeger\big) = V_{TO} + \gamma\left(\sqrt{(2\phi_{F} - V_{BS})} - \sqrt{2\phi_{F}}\right) \quad \text{(for n-channel devices)} \\ &V_{T}\big(Pierret\big) = V_{TP}\big(Jaeger\big) = V_{TO} - \gamma\left(\sqrt{(2\phi_{F} + V_{BS})} - \sqrt{2\phi_{F}}\right) \quad \text{(for p-channel devices)} \\ &\text{where,} \end{split}$$

$$\gamma = \frac{\sqrt{2qN_A \varepsilon_S}}{C_{or}}$$

is known as the **body effect parameter**

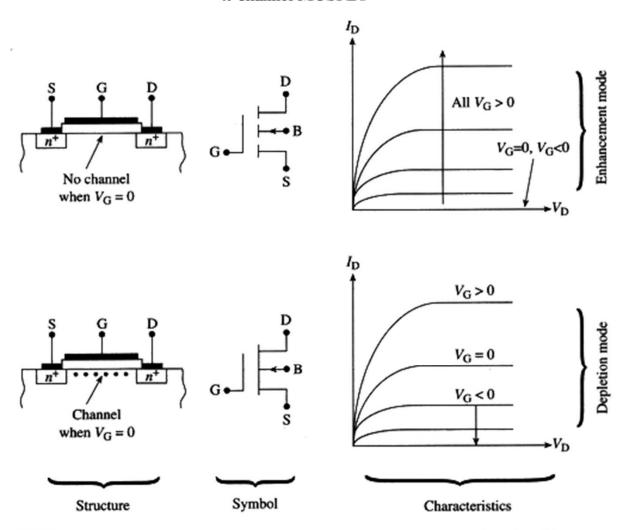

## Enhancement Mode verses Depletion Mode MOSFET

We have been studying the "enhancement mode" MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor). It is called "enhancement" because conduction occurs only after the channel conductance is "improved" or "enhanced". In this case,

$$V_{TN} > 0$$

and  $V_{TP} < 0$

Transistors can be fabricated such that:  $V_{TN} \le 0$  and  $V_{TP} \ge 0$

These transistors have conduction for  $V_{GS}$ =0 due to a channel already existing without the need to "invert the near surface region". To modulate currents, a field must applied to the gate that depletes the channel. Thus, transistors of this nature are called "Depletion mode MOSFETs".

## Enhancement Mode verses Depletion Mode MOSFET

n-channel MOSFET

MOSFET operational modes.  $V_{\rm G}=0$  channel status, circuit symbol, and  $I_{\rm D}-V_{\rm D}$  characteristics of *n*-channel enhancement-mode and depletion-mode MOSFETs.

# MOS Transistor: Summary

|                     | 4-Terminal            |                       | 3-Terminal  |                       |

|---------------------|-----------------------|-----------------------|-------------|-----------------------|

|                     | Enhancement           | Depletion             | Enhancement | Depletion             |

| NMOS<br>(n-channel) | $G \longrightarrow B$ | $G \longrightarrow B$ |             | $G \longrightarrow S$ |

| PMOS (p-channel)    | $G \longrightarrow B$ | $G \longrightarrow B$ | c s s       | c s                   |

## Jaeger uses the notation:

**NMOS**

$$K_n = K_n \frac{W}{L} = \overline{\mu_n} C_{ox} \frac{W}{L}$$

where W is the Gate Width (Z in Pierret)

**PMOS**

$$K_p = K_p \frac{W}{L} = \overline{\mu_p} C_{ox} \frac{W}{L}$$

where W is the Gate Width (Z in Pierret)

## MOS Transistor: Summary

|                                        | NMOS                                                                                                                                                                                                          | PMOS                                                                                                                                                                          |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Regardless of Mode                     | $K_n = K_n \frac{W}{L} = \overline{\mu_n} C_{ox} \frac{W}{L}$ (Note: W = Z in Pierret)                                                                                                                        | $K_p = K_p \frac{W}{L} = \overline{\mu_p} C_{ox} \frac{W}{L}$ (Note: W = Z in Pierret)                                                                                        |

| Cutoff                                 | $I_{DS} = 0$ for $V_{GS} \le V_{TN}$                                                                                                                                                                          | $I_{DS} = 0$ for $V_{GS} \ge V_{TP}$                                                                                                                                          |

| Linear                                 | $I_{DS} = \frac{Z\overline{\mu_n}C_{ox}}{L} \left[ (V_{GS} - V_{TN})V_{DS} - \frac{V_{DS}^2}{2} \right]$ $V_{GS} \ge V_{TN}  and  V_{GS} - V_{TN} \ge V_{DS} \ge 0$                                           | $I_{D} = \frac{Z\overline{\mu_{n}}C_{ox}}{L} \left[ (V_{GS} - V_{TP})V_{DS} - \frac{V_{DS}^{2}}{2} \right]$ $V_{GS} \leq V_{TP}  and   V_{GS} - V_{TP}  \geq  V_{DS}  \geq 0$ |

| Saturation                             | $\begin{split} I_{DS} &= \frac{Z\overline{\mu_n}C_{ox}}{2L} \Big[ \big(V_{GS} - V_{TN}\big)^2 \Big] \big(1 + \lambda V_{DS}\big) \\ V_{GS} &\geq V_{TN}  and  V_{DS} \geq V_{GS} - V_{TN} \geq 0 \end{split}$ | $I_{DS} = \frac{Z\overline{\mu_n}C_{ox}}{2L} [(V_{GS} - V_{TP})^2] (1 + \lambda  V_{DS} )$ $V_{GS} \le V_{TP}  and   V_{DS}  \ge  V_{GS} - V_{TP}  \ge 0$                     |

| Threshold Voltage                      | $V_{TN} = V_{TO} + \gamma \left( \sqrt{\left(2\phi_F + V_{SB}\right)} - \sqrt{2\phi_F} \right)$                                                                                                               | $V_{TP} = V_{TO} - \gamma \left( \sqrt{\left(2\phi_F + V_{BS}\right)} - \sqrt{2\phi_F} \right)$                                                                               |

| V <sub>T</sub> for Enhancement<br>Mode | $V_{TN} > 0$                                                                                                                                                                                                  | $V_{TP} < 0$                                                                                                                                                                  |

| V <sub>T</sub> for Depletion<br>Mode   | $V_{\scriptscriptstyle TN} \leq 0$                                                                                                                                                                            | $V_{TP} \ge 0$                                                                                                                                                                |

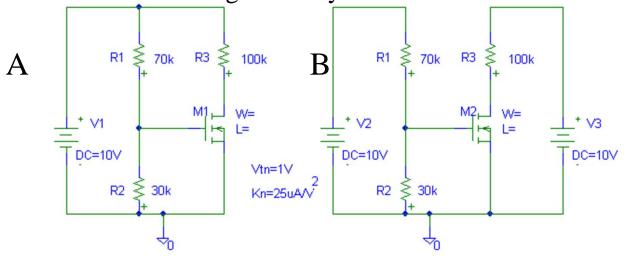

## Bias Circuitry-Enhancement Mode NMOS

Due to zero DC current flow in the gate, the bias analysis of a MOSFET is significantly easier than a BJT.

•Form Thevenin circuits looking out the gate, drain, and source

Georgia Tech

\_ CE 3040 - Dr. Alan Doolittle

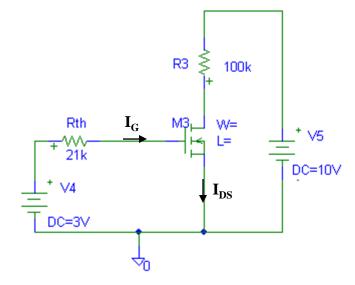

## Bias Circuitry-Enhancement Mode NMOS

$$3V = I_G R_{th} + V_{GS}$$

$$10V = I_{DS} R3 + V_{DS}$$

- •But  $I_G=0$  so  $V_{GS}=3V$

- •Assume Saturation operation (selected for easy math because  $I_{DS}$  does not depend on  $V_{DS}$  since no  $\gamma$  was given  $\gamma$ =0):

$$i_{DS} = \frac{K_n}{2} \left[ (v_{GS} - V_{TN})^2 \right] for \quad v_{DS} \ge v_{GS} - V_{TN} \ge 0$$

$$i_{DS} = \frac{25x10^{-6}}{2} \left[ (3-1)^2 \right] = 50\mu A$$

$$Check V_{DS}$$

$$10V = 50uA(100k) + V_{DS}$$

$$V_{DS} = 5V > V_{GS} - V_{TN} = 2V$$

•Assumption of Saturation operation was correct! If it were not correct simply make another assumption (I.e. linear region) and resolve.

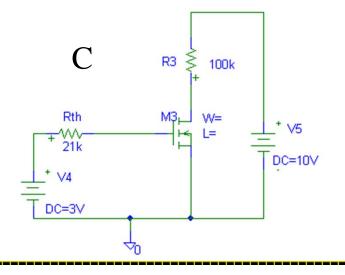

### Bias Circuitry-Depletion Mode NMOS

•Bias circuit of a depletion mode device is much simpler due to the fact that the device conducts drain current for  $V_{GS}$ =0V

$$V_{TO} = -3V$$

$$\gamma = 0\sqrt{V}$$

$$K_n = 200 \quad uA/V^2$$

$$R1 \leq 20k$$

- •What value of R1 results in 100 uA drain current?

- •Again Assuming saturation:

$$i_{DS} = \frac{K_n}{2} \left[ (v_{GS} - V_{TN})^2 \right] for \quad v_{DS} \ge v_{GS} - V_{TN} \ge 0$$

$$V_{GS} = V_{TN} + \sqrt{\frac{2I_{DS}}{K_n}} = -3V + \sqrt{\frac{2(100uA)}{200uA/V^2}} = -2V$$

$$R1 = -\frac{V_{GS}}{I_{DS}} = -\frac{-2}{100uA} = 20 \ K\Omega$$

$$Check \ V_{DS}$$

$$10V = I_{DS} R1 + V_{DS} = 100uA(20k) + V_{DS}$$

$$V_{DS} = 8V > V_{GS} - V_{TN} = -2V - (-3V) = +1V$$

•Assumption of Saturation operation was correct! If it were not correct simply make another assumption (I.e. linear region) and resolve.

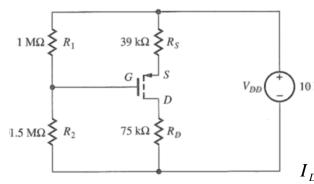

Bias Circuitry-Enhancement Mode PMOS

$$V_{TO} = -1V$$

$$\gamma = 0\sqrt{V}$$

$$K_p = 25 uA/V^2$$

$$I_{D} = I_{S} = \frac{Z\overline{\mu_{n}}C_{ox}}{2L} [(V_{GS} - V_{TP})^{2}] (1 + \lambda |V_{DS}|) = \frac{K_{p}}{2} [(V_{GS} - V_{TP})^{2}]$$

$$V_{GS} \leq V_{TP} \quad and \quad |V_{DS}| \geq |V_{GS} - V_{TP}| \geq 0$$

$$\begin{split} V_{EQ} &= 10V \frac{1.5M}{1.5M + 1M} = 6V \quad R_{EQ} = 1M \mid \mid 1.5M = 600K\Omega \\ V_{DD} &= I_S R_S - V_{GS} + I_G R_G + V_{EQ} \\ V_{DD} - V_{EQ} &= R_S \frac{K_p}{2} \Big[ (V_{GS} - V_{TP})^2 \Big] - V_{GS} \\ 10 - 6 &= 4 = 39,000 \frac{25E - 6}{2} \Big[ (V_{GS} + 1)^2 \Big] - V_{GS} \\ V_{GS}^2 - 0.051V_{GS} - 7.21 &= 0 \quad \Rightarrow V_{GS} = +2.71 \ or - 2.66V \\ I_D &= \frac{25E - 6}{2} \Big[ (-2.66 + 1)^2 \Big] = 34.4\mu A \\ V_{DD} &= I_D R_S - V_{DS} + I_D R_D \quad \Rightarrow V_{DS} = -6.08V \\ Check V_{DS} \\ |V_{DS}| \geq |V_{GS} - V_{TP}| \geq 0 \quad \Rightarrow |-6.08| \geq |-2.66 - (-1)| \geq 0 \end{split}$$

$R_{\rm S} \gtrsim 39 \,\mathrm{k}\Omega$

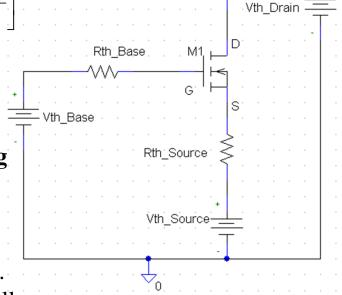

### Bias Circuitry-Possible Combinations

1)

$$V_{th\_Base} = V_{GS} + I_{DS}R_{th\_Source} + V_{th\_Source}$$

2)

$$I_{DS} = \frac{K_n}{2} \left[ (V_{GS} - V_{TN})^2 (1 + \lambda V_{DS}) \right]$$

or  $I_{DS} = K_n \left[ (V_{GS} - V_{TN}) V_{DS} - \frac{V_{DS}^2}{2} \right]$

and optionally, Assume either saturated or linear/triode.

3)

$$V_{th\_Drain} = V_{DS} + I_{DS} \left( R_{th\_Source} + R_{th\_Drain} \right) + V_{th\_Source}$$

- •Always: Solve 1) for  $V_{GS}$  and plug into 2).

- •In certain cases,  $V_{DS}$  will need to be eliminated by using 3) solved for  $V_{DS}$  and plugged into 2).

- •Case A: Saturated, and  $\lambda$ =0 and no source resistor only 1 and 2 required. Results in 1<sup>st</sup> order polynomial.

- •Case B: Saturated, and  $\lambda>0$  and no source resistor all 3 equations needed. Results in 1<sup>st</sup> order polynomial.

- •Case C: Saturated, and  $\lambda$ =0 and a source resistor all 3 equations needed. Results in 2<sup>nd</sup> order polynomial.

- •Case D: Saturated, and  $\lambda$ >0 and a source resistor all 3 equations needed. Results in 3<sup>rd</sup> order polynomial.

- •Case E: Linear/Triode, with or without a source resistor

- all 3 equations needed. Results in 2<sup>nd</sup> order polynomial.

#### Useful Formulas for DC Bias Solutions

If a 3<sup>rd</sup> order polynomial results, try factoring it into a linear and quadratic term 1<sup>st</sup>. If this is not easy for your case, a longer but sure fire way is listed below.

#### QUADRATIC EQUATIONS

Any quadratic equation may be reduced to the form,-

$$ax^2 + bx + c = 0$$

Then

$$x = \frac{-b \pm \sqrt{b^2 - 4ac}}{2a}$$

If a, b, and c are real then:

If  $b^2 - 4ac$  is positive, the roots are real and unequal;

If  $b^2 - 4ac$  is zero, the roots are real and equal;

If  $b^2 - 4ac$  is negative, the roots are imaginary and unequal.

#### **CUBIC EQUATIONS**

A cubic equation,  $y^3 + py^2 + qy + r = 0$  may be reduced to the form,—

$$x^3 + ax + b = 0$$

by substituting for y the value,  $x - \frac{p}{3}$ . Here

$$a = \frac{1}{3}(3q - p^2)$$

and  $b = \frac{1}{27}(2p^3 - 9pq + 27r)$ .

For solution let,-

$$A = \sqrt[3]{-\frac{b}{2} + \sqrt{\frac{b^2}{4} + \frac{a^3}{27}}}, \qquad B = -\sqrt[3]{+\frac{b}{2} + \sqrt{\frac{b^2}{4} + \frac{a^3}{27}}},$$

then the values of x will be given by,

$$x = A + B$$

,  $-\frac{A + B}{2} + \frac{A - B}{2} \sqrt{-3}$ ,  $-\frac{A + B}{2} - \frac{A - B}{2} \sqrt{-3}$ .

If p, q, r are real, then:

If  $\frac{b^2}{4} + \frac{a^3}{27} > 0$ , there will be one real root and two conjugate complex roots;

If  $\frac{b^2}{4} + \frac{a^3}{27} = 0$ , there will be three real roots of which at least two are equal;

If  $\frac{b^2}{4} + \frac{a^3}{27} < 0$ , there will be three real and unequal roots.